Overview of Processus Semiconductor

Processus semiconductor principaliter involvit applicando microfabricationem et technologias pelliculas ad astulas et alia elementa intra varias regiones plene connectendas, qualia sunt subiecta et tabulae. Hoc faciliorem reddit extractionem plumbi terminalum et encapsulationis cum medio plastic insulating ad totum integratum formandum, ut tres dimensiva structurae exhibetur, tandem processum fasciculum semiconductorem complens. Notio processus semiconductoris etiam ad strictam definitionem semiconductoris chip packaging pertinet. Ex latiore prospectu, ad machinationem machinalem refertur, quae connectens et defigendo implicat subiectam, congruentem electronic apparatum conformans et systema completam magnis effectibus comprehensivis construens.

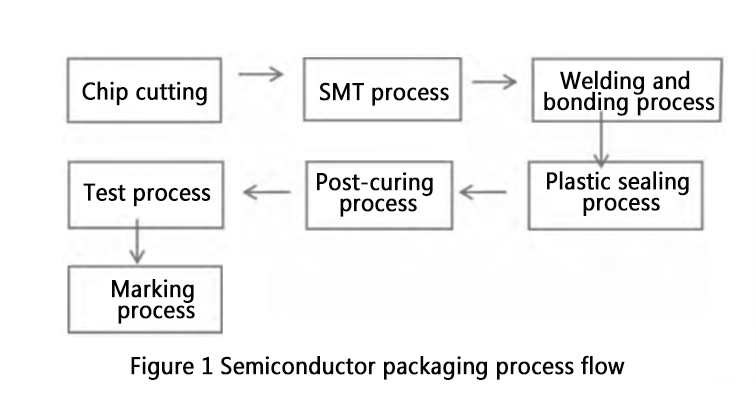

Semiconductor Packaging Process flow

Semiconductor processum packaging multiplex munia includit, sicut in Figura illustratur 1. Singulae processus peculiares exigentias et operas propinquas habent, accuratam analysin in scaena practica necessariam habent. Contentum specificum hoc modo est:

1. Chip secans

In processu fasciculi semiconductoris, chip secans involvit lagana siliconis in singula astulas et statim obstantia Pii removens ne impedimenta operis et qualitatis subsequentis coerceant.

2. Chip Adscendens

Chip processum ascendens spectat ad evitandum damnum circa laganum stridor applicando stratum cinematographicum tutelae, constanter in luce circuii integritatem.

3. Filum Bonding Processus

Refrenans qualitatem fili compagis processus implicat utens diversis generibus filis aureis ad ligamen pads cum compage pads coniungendi, ut chip in gyros externos coniungere potest et altiore processu integritatem conservans. De more, sertis filis aureis et filis aureis commixtis adhibitis.

Fila aurea emissa: Genera includunt GS, GW, TS, apta arcui magno (GS: >250 μm), arcui medio-alto (GW: 200-300 µm), et arcui medio-low (TS: 100-200 μm) vinculum respectively.

Fila aurea commixta: Genera includunt AG2 et AG3, compaginationem arcus humilem aptam (70-100 µm).

Diameter bene pro his filis ab 0.013 mm usque ad 0.070 vagantur. Formam aptam eligendo et diametros in operationibus exigentiis et signis innixus crucial pro qualitate temperantiae.

4. CUMATIUM Processus

Praecipua circuitus in fingendis elementis encapsulationis implicat. Processus fingens qualitatem moderans componentes protegit, praesertim ab copiis externis variis damni gradus causantibus. Hoc involvit penitus analysin partium physicarum proprietatum.

Tres modi principales currently adhibentur: ceramic packaging, plasticus sarcina, ac traditum packaging. Proportio administrandi cuiusque generis sarcinae pendet obviam productio chip globali postulat. In processu, facultates comprehensivae requiruntur, ut preheating chip et plumbum corpus ante encapsulation cum resina epoxy, corona et post-forma curationis.

5. Post-Curing Processus

Post coronarium processum, curatio post curationem requiritur, superflua materias circa processum vel sarcinam amovens. Moderatio qualitatis essentialis est ad vitandum altiorem processum qualitatem et speciem afficiendi.

6.Testing processu

Postquam superiores processus perfecti sunt, altiore qualitate processuum probata est utendi technologiae probatae et facultates. Hic gradus involvit singula recordationem notitiarum, intentus num normaliter opus chip in gradu suo perficiendi. Cum magno apparatu probati instrumenti, maximum est conservare qualitatem dominii per gradus producendi, incluso inspectione visivae et electricae operationis probatio.

Electrical euismod Testis: Hoc involvit probationes ambitus integrales utens instrumenti automatico experimento et ad unumquemque ambitum praestandum apte connexum pro electrico experimento.

Visual Inspectio: technici microscopiis utuntur ut astulas sarcinas confectas penitus inspiciant ut a defectibus immunes sint et signa qualitatis semiconductoris packaging.

7. Vestigium Processus

Processus notationis involvit probatum astulas transferre ad horreum semi-perfectum pro processui finali, inspectione, packaging, et de naviculas. Hic processus tres principales gradus includit:

1) Electroplating: Post formationem ducum applicatur materia anti-corrosio ad praecavendam oxidationem et corrosionem. Depositio technologiae electroplating typice usus est, cum pleraque plumbi e stagno fiunt.

2) Flexio: Ducit processionaliter tunc formatur, cum ambitus integratis habena in instrumento plumbeo formante positae, figuram plumbeam continentes (J vel L typus) et fasciculum superficiei insidentem.

3) Laser Printing: Denique producta formata cum consilio impressa sunt, quae peculiari nota est pro processu fasciculi semiconductoris, sicut in Figura III illustratur.

Provocationes et Commendationes

Studium processuum fasciculorum semiconductoris incipit cum contemplatione technologiae semiconductoris ad sua principia intelligenda. Deinceps explorans processum fasciculum fluere intendit curare ut sollicita moderatio in operationibus adhibens exquisita administratione ad quaestiones exercitationis vitandas. In contextu hodiernae evolutionis, provocationes in semiconductoribus processuum packaging identificatio essentialis est. Commendatur ut rationes qualitatum imperium intendunt, cardinis penitus dominantur ut processum qualitatis efficaciter augeant.

Ex consideratione qualitatum perspectiva moderatio, provocationes significantes sunt in exsecutione propter multiplices processus cum argumentis et requisitis specificis, invicem influentes. Imperium rigidum necessarium est in operationibus practicis. Per meticulosos habitus operis adhibito ac technologias provectas applicando, semiconductorem processum packaging qualitatem et gradus technicos emendari potest, ad effectum deducendi applicationis comprehensivam efficaciam ac praestantia altiore utilitates assequendas (ut in fig. 3).

Post tempus: May-22-2024