1.About Integrated Circuits

1.1 De conceptu et partu ambituum integratorum

Circuitus integratus (IC): refertur ad machinam quae machinis activis componit sicut transistores et diodes cum passivis componentibus sicut resistores et capacitores per seriem technicorum specificarum processus.

Circuitus seu systema quod "integratum" est in semiconductore (ut silicon vel composito ut gallium arsenide) laganum secundum certas connexiones circa ambitum et deinde in concha involucrum ad functiones specificas praestandas.

Anno 1958, Jack Kilby, qui miniaturizationem instrumentorum electronicorum instrumentorum Texas instrumentorum (TI) author erat, notionem circuitionum integralium proposuit:

"Cum omnia elementa, ut capacitores, resistores, transistores, etc. ex una materia fieri possunt, putavi posse eas facere in materia semiconductoris, et deinde eas coniungi ad totum ambitum formare."

Die 12 Septembris et 19 Septembris 1958, Kilby fabricam et demonstrationem perfecit oscillatoris et felis Phase, respective, nativitatem ambitus integrati notans.

Anno 2000, Kilby Praemium Nobelianum in Physicis consideratum est. Praemium Nobelianum Committee olim commentatus est Kilby "fundamentum pro modernis informationibus technologiarum".

Pictura infra ostendit Kilby et eius ambitus patentes integrales;

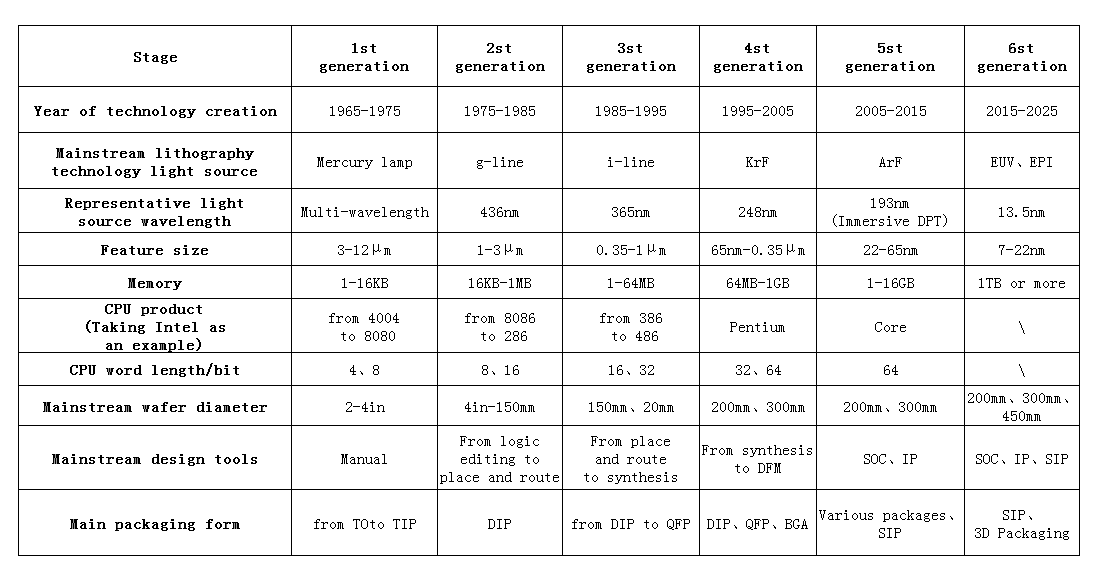

1.2 progressio semiconductor fabricandi technologiae

Sequens figura technologiae technologiae evolutionis gradus semiconductoris ostendit;

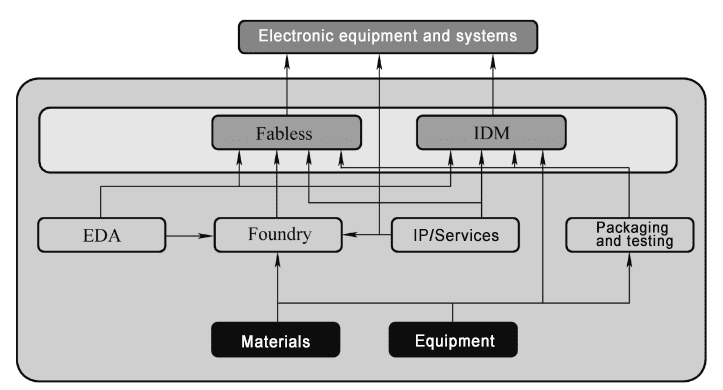

1.3 Integrated Circuit Industry Chain

Compositio semiconductoris industriae catenae (circuitus maxime integrati, machinis discretis inclusis) in figura supra monstratur;

- Fables: Congregatio quae producta designat sine linea productiva.

- IDM: Integrated Fabrica Fabrica, integrata fabrica fabrica;

- IP: Circuitu moduli opificem;

- EDA: Electronic Design Automatic, electronic design automation, societas maxime consilio instrumenta praebet;

- Pretium; Azymum liquatur, praebens operas chippis fabricandae;

- Packaging ac probatio forensium societatum: maxime servientes Fables et IDM;

- Materias et turmas apparatu speciali: maxime praebent necessarias materias et apparatum pro societatibus fabricandis chippis.

Summa productorum productorum usus technologiae semiconductoris ambitus integrae sunt et cogitationes semiconductor discretae.

Summa productorum ambituum integratorum includit:

- Application Imprimis Partes Standard (ASSP);

- Microprocessor Unit (MPU);

- Memoria

- Application Imprimis Integrated Circuit (ASIC);

- Analog Circuit;

— Circuitus Logicae Generalis (Logic Circuit).

Summa products semiconductoris discretae cogitationes includit:

— Diode;

— Transistor;

- Power Fabrica;

- Summus intentione Fabrica;

- Proin Fabrica;

- Optoelectronics;

- Sensor Fabrica (Sensor).

2. Integrated Circuit vestibulum Processus

2.1 Vestibulum Chip

Dozens vel etiam decem milia astularum specificarum simul in laganum silicum fieri possunt. Numerus xxxiii in lagano silico pendet a specie producti et pro cuiusque spumae magnitudine.

lagana Pii substrata dicuntur. Diameter laganae siliceae plusquam annis ab initio minus quam 1 pollicis ad 12 digitos (circiter 300 mm) nunc increscit, et transitum patitur ad 14 pollices vel 15 pollices.

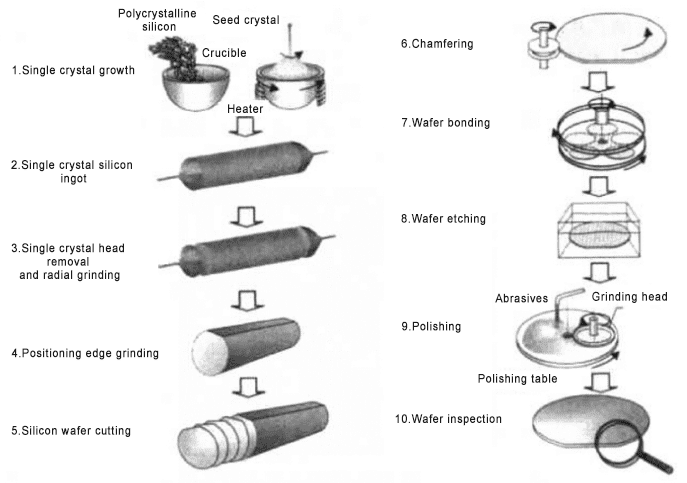

Chip fabricandis plerumque in quinque gradus dividitur: praeparatio lagani siliconis, vestibulum laganum pii, chip probatio/legendi, conventus et sarcina, et probatio finalis.

(1)

Praeparatio laganum Pii:

Ad materiam crudam, Pii ex arena extrahitur et purificatur. Peculiaris processus pii diam propriae ingots producit. Stipulae deinde in tenues laganas silicae ad microchips faciendas incisae sunt.

Lagana parata sunt ad specificationes specificas, sicut ad marginem adnotationem requisita et gradus contagione.

(2)Pii laganum vestibulum:

Etiam nota ut vestibulum chip, nudum laganum pii ad plantam vestibulum lagani pii pervenit et deinde per varias purgatio, formatio cinematographica, photolithographia, etching et doping vestigia. Silicon laganum processit cum lagano perfecto statuto circulorum integratorum in lagano silicone haerens perpetuo est.

(3)Testis et electio uncta Pii:

Post confectum laganum laganum vestibulum, lagana silicon mittuntur ad aream amussim, ubi singula astulae rimantur et electrically experti sunt. Acceptum et acceptum astulas tunc digestae sunt, et astulae defectivae signatae sunt.

(4)Conventus et packaging:

Post laganum experimentum/dificium, laganum in ecclesiam intrant et gressum packaging ad sarcinas singulas astulas in sarcinis tubi tutelares. Tergum laganum teritur ad crassitudinem redacti.

Pellicula densa plasticae dorsi cuiusque lagani adnectitur, et deinde ferrum serrae adamantinae praefixae ad laganum laganum secundum lineas scribae in parte anteriori separare solebat.

Pellicula plastica in dorso lagani Pii custodit spumam siliconis ne defluat. In planta conventus, boni astuli pressi vel emissi ad sarcinam conventus formandam. Postea, chip signatum est in testa plastic vel tellus.

(5)Test finalis:

Ut ad functionem capitis chip, singulae ambitus integrales fasciculi inveniant, temptatur obviam normae notae fabricae electricae et environmental parametri requisita. Post ultimam probationem, chip mittitur ad emptorem pro contione in loco dedicato.

2.2 Processus Division

Processus fabricandi ambitus integrati plerumque in dividuntur;

Ante-finem: Processus anterioris finis plerumque refertur ad processum fabricationis machinis sicut transistores, maxime incluso processibus formationis solitariae, structurae portae, fontium et exhaurientium, contactuum foraminum, etc.

Retro-finemProcessus posterioris-finis principaliter refertur ad linearum connexionis formationem quae electricas signa in varias machinas in spumam transmittere potest, praesertim in processibus ut dielectricae depositionis inter lineas connexionis, lineae metallicae formationis, et plumbi caudex formationis.

Proin tempus: Ad emendandum transistorum perficiendorum nodis technologiae progressus post 45nm/28nm portae dielectrics et processibus metallicis portae altae utuntur, ac postea portae processus adde et processibus localibus connexis post transistoris fontem et structuram exhauriunt praeparata. Hi processus sunt inter processum ante-finem et posticum in processu, et in processibus traditis non adhibentur, ideo vocantur processus medius.

Fere processus contactus foraminis praeparationis dividens lineam est inter processum anteriorem et finem processus posterioris.

Contactus foramen: foramen verticaliter in laganum pii impressum ad connectendum primam connexionem metalli iacuit et fabricam subiectam. Metallo ut tungsten repletum est et machinam electrode ducere ad connexionem metallicam adhibetur.

per foramen: Connexio est via inter duas stratas metallicas lineas interiectas, in strato dielectric inter duas stratas metallicas positam, et plerumque metallis sicut aeris repleta est.

In sensu lato;

Processus ante-finemIn lato sensu, ambitus fabricationis integralis comprehendere debet probatio, packaging et alii gradus. Comparata cum probatione et packaging, componentibus et connexis fabricandis, sunt prima pars fabricationis circuli integralis, collective ad processuum ante-finem;

Back-finem processus: Temptatio et packaging processus ad finem vocantur.

3. Appendix

SMIF:Standard Mechanica interface

AMHS:Automated Material tradendi Ratio

OHT caput Levate TRANSFERENDIS

FOUP:Front foramen Unified Pod,exclusive ad XII pollicis 300mm) lagana

Potius,Semicera potest provideregraphite partes, mollis / rigidus sensit ;Pii partes carbide, CVD pii partes carbideetSiC/TaC iactaretcum pleno processu semiconductoris in XXX diebus.Sincere nos expectamus ad longum tempus socium tuum in Sina fieri.

Post tempus: Aug-15-2024